This would likely not be efficient in an single-FPGA design as that testbench would use a significant chunk of the FPGA’s resources. In ASIC designs we tended to make our testbenches synthesizeable so they could be tested in an FPGA implementation.This is obviously not necessary for an FPGA-based design verification is likely handled as a software task which feeds test inputs to the FPGA. ASIC designs are normally modeled in an FPGA-board implementation (we used Quickturn).In ASICs, you produce a set of reticle layer patterns (GDSII files). You are bound by the number of FPGA Assets (LUTS/DSP Multipliers/etc). In FPGAs, your final implemenatation comes in the form of a bit/xsvf file which is uploaded to the FPGA, either in an SRAM pattern or a Flash/Fuse pattern. Otherwise you will probably violate setup on a flop and the simulators I have used have not modeled metastability. If you are dealing with asynchronous clock domains, you will probably need to squelch the clock-boundary-crossing setup/hold times or run with a synchronous clock (or run a two-state simulation).This is less likely in an FPGA because the process libraries are far more widely used and so errors are likely caught a lot earlier. Your SDF file may not match your gate-level generic parmeters.You probably didn’t capture waveforms for every internal signal you needed, forcing a rerun (I’ve had this take weeks).They are very slow, because you are simulating many more elements.The major issues with the simulations are: Verification of external memory or peripheral access timings against a vendor-provided model.This caused unknowns in simulation which we wouldn’t have caught in RTL simulation. I once had a synthesis library which had allowed a flop to have both its SET and CLEAR bits set.Among the other cases where I’ve needed to do this: I have usually done these as a final QC step. Give the tool only as much information it needs to get the job done.

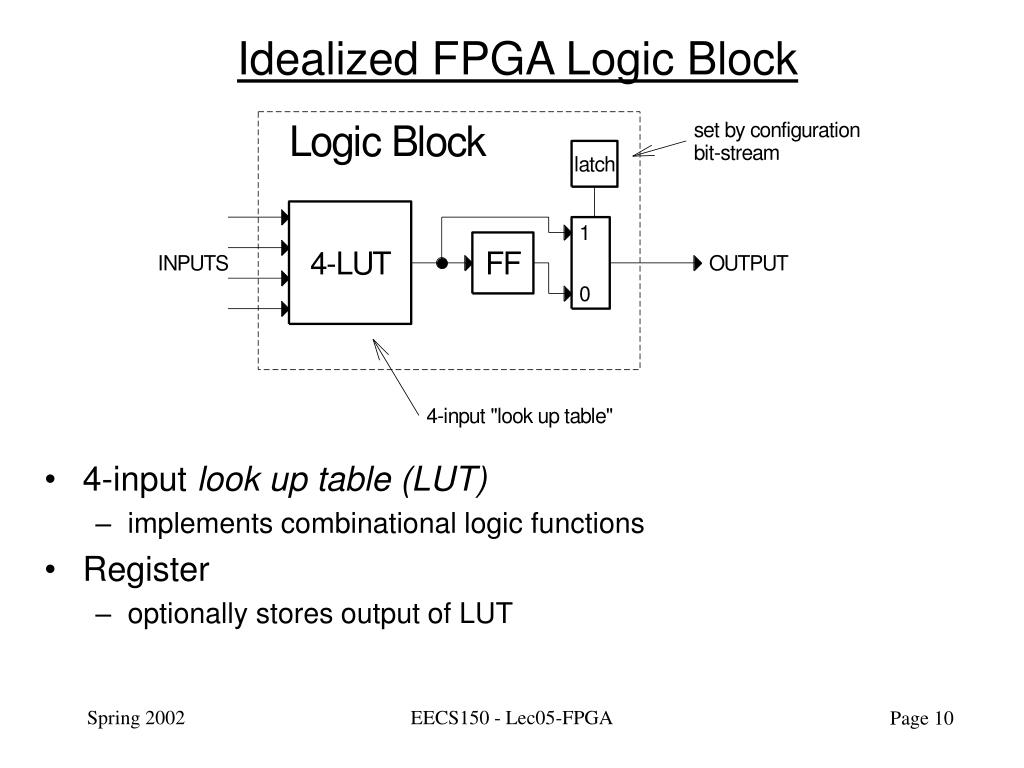

Floorplan Design – Give the implementer ‘hints’ on where to place circuits for optimal timing.Implement Design – Now, take your design and implement (choose the actual locations for cell placement or LUT setting).Simulate gate-level netlist, to verify the RTL was properly mapped to gates.Synthesize Design – map the design into ASIC Cells or LUTs/FPGA Assets.Elaborate Design – turn the design into a “generic” technology to make sure your Verilog is synthesizeable.I’ve been using Verilator because I believe it is faster and allows me a better interface to compiled software which might interface with an FPGA. FPGAs tend to come with packaged IPs specific to their use which presumably use the LUTs/DSP slices more effectively. The initial steps of FPGA and ASIC design are essentially the same: I acquired a ZYNQ TUL-2 Board Board, which is a processor-FPGA Hybrid containing a dual-core ARM interfacing to an FPGA Fabric. With my background in ASIC design, I decided to start pursuing FPGA Design as a serious hobby.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed